MicroBlazeの組み込み方(セミナ受講して復習してみました)

9月 28, 2012 コメントを残す

本日、大崎にある新光商事さんへ行き、「MicroBlaze」のミニセミナを受講してきました。

そこで学習したものを、弊社所有のVC707で復習がてら忘れないために行ってみました。

はっきり言って手順をそのまま箇条書きのように書いているので、大量、見づらい、読みにくいですが、かなり細かく書きました。

-

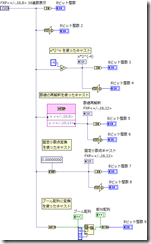

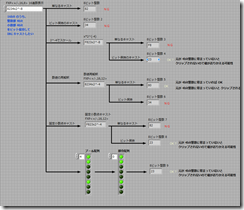

流れの解説

一通りの流れを以下に示す。

|

流れ |

ツール |

アクションと目的 |

|

① |

ISE |

プロジェクト作成、全体のプロジェクトを作成する |

|

② |

ISE |

新規EDKプロジェクトソース追加、MicroBlazeコア部分。EDKが起動する。 |

|

③ |

EDK |

EDK起動後、BSBウィザードで MicroBlaze に関する各種初期設定を行う。これが MicroBlaze部分の開発。 |

|

④ |

ISE |

トップレベル階層の VHDL を自動で作成し、コンパイル。 |

|

⑤ |

ISE |

SDKの為の HW デザインをエクスポートする。 |

|

⑥ |

SDK |

SDKで Cプロジェクトを作成する。 |

|

⑦ |

SDK |

Cソースを作成し、elf ファイルを作る。 |

|

⑧ |

SDK |

ボード上で走らせデバッグする |

|

⑨ |

ISE |

MicroBlaze プログラム (elf)を含めて ISE でコンパイルし 最終ビットファイルを作成する。 |

|

⑩ |

IMPACT |

プログラミングして実行。 |

-

作成するもの

ボード上の ボタンを押すと 対応するLED が点灯するというプログラムを MicroBlaze上で動かす。

[23]のボタンで、[22]の LED を点灯させる。

-

手順

- ISE: ISEを起動し、プロジェクトを作成する。

ISE 14.2 を起動する。

ダブルクリック

ISE 起動

[File] → [New Project]

[Name] は TestVC707 にした。

[Location]は適宜。

[Next] ボタン

Project Setting では、デバイスなどの情報を設定する。

今回は、もともと VC707 という「ボード」がサポートされているので、[Evaluation Development Board] で [Virtex-7 VC707 Evaluation Platform] を選択。

[Next]ボタン

サマリが表示されるので [Finish] ボタン

Hierarchy に VC707 のデバイスが表示される。

- ISE: ISEプロジェクトに、新規 EDK プロジェクトソースを追加する。

[Project]メニュー→[New Source…]

[Embedded Processor] を選び、File name には SYSTEM とつけた。

Location はそのまま。Add to project はチェックが入っている状態で

[Next]ボタン

サマリが表示されるので [Finish] ボタン

すると、しばらく EDK ファイルを作成し、 EDK (Xilinx Platform Studio) が起動する。

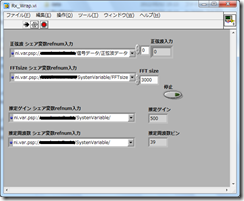

- EDK: EDK起動後、BSBウィザードで MicroBlaze に関する各種初期設定を行う。

BSB Wizard で作るか聞いてくるので [Yes]

使うバスタイプを決める。Virtex7 では AXI(アクシーと発音) しか選べない。

[OK] ボタン

ボード情報があるかどうかなので、あるので、そのまま[Next]

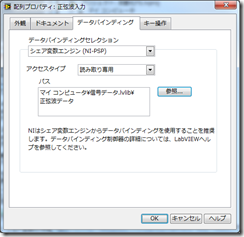

ここでは、プロセッサ、ペリフェラルの設定ができる。

上から、プロセッサの周波数。50/100/150 MHz を選択できる。

とりあえず 100MHz で。

Local Memory 、Instruction/ Data Cache は 8kB で。

ペリフェラル関連は、コンパイル時間を短くするために、

LEDs_8Bits

Push_Buttons_5Bits

以外は Remove

で[Finish]

EDK のプロジェクトを作成中。。。

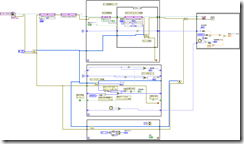

終わるとこんな画面。

この時点で、この SYSTEM の UCFが作成されている。

”SYSTEM\data" フォルダに "SYSTEM.ucf" ができている。

本来、ここでバスにぶら下げる IP を追加したりするが、今回はとりあえずこれで終了処理。

EDK を閉じる。

- ISE: トップレベル階層の VHDL を自動で作成。UCF追加してコンパイル。

ISE に戻り、トップレベルの VHDL を作成する。(そのままではコンパイルできないので、ラッパーを作成するということ)

Hierarchy で先程作成した SYSTEM (SYSTEM\SYSTEM.xmp) をハイライトする。

Process: SYSTEM で、[Generate Top HDL Source] をダブルクリック。

作成できると、Hierarchy には SYSTEM_top.vhd が追加され、先程の SYSTEM はその下に入る。

[Project]メニュー->[ADD Source] で SYSTEM\data\SYSTEM.ucf を追加。

チェック OK なので、[OK]ボタン

Hierarchy に追加された。

ここで、SYSTEM.ucf を一部修正する。

この UCF の最後から2行目

の "CLK" を "CLK_P" にする。

なぜ修正するかは、吐き出された UCF のタイミングのネット名 "CLK" が本来の差動で定義されている "CLK_P" と "CLK_N" にあっていないから。

全て保存して、Hierarchy の SYSTEM_top を選択。

Processes: SYSTEM_top – STRUCTURE の [Generate Programming File] をダブルクリック。

まつこと数十分

結果抜粋

|

Slice Logic Utilization |

Used |

Available |

Utilization |

|

Number of occupied Slice |

750 |

75,900 |

1% |

|

Number of RAMB36E1/FIFO 36E1s |

2 |

1,030 |

1% |

|

Number of BUFG/BUFGCTRLs |

2 |

32 |

6% |

|

Number of DSP48E1s |

3 |

2,800 |

1% |

|

Number of MMCME2_ADVs |

1 |

14 |

7% |

これで、MicroBlaze を組み込んだ FPGA 全体が完成する。

ただし、プログラムがないので、SDKで作成する。

- ISE: SDKの為の HW デザインをエクスポートする。

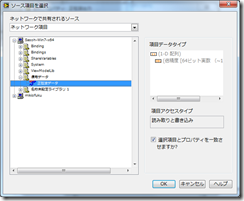

SDK で MicroBlaze のプログラムを組むために、 ISE から HW デザインを エクスポートする。

Hierarchy で SYSTEM_i – SYSTEM (SYSTEM\SYSTEM.xmp) をハイライト。

Processes: SYSTEM_i – SYSTEM で [Export Hardware Design To SDK with Bitstream" をダブルクリック。

成功すると SDK が起動する。

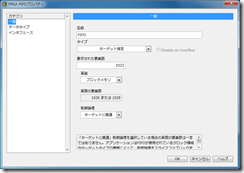

- SDK: SDKで Cプロジェクトを作成する。

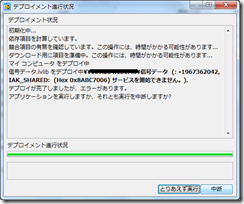

起動すると以下のダイアログが表示される。

SDK のワークスペースを指定する。

ISE のプロジェクトフォルダ内の、"SYSTEM\SDK\SDK_Export" を選ぶ。

こんなような SDK の開発環境の画面が開く。

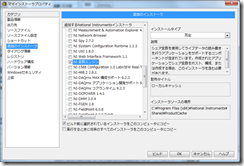

とりあえず何もないので、Cプロジェクトを作成するウィザードを実行する。

[File]メニュー→[New] → [Xilinx Cproject]

デフォルトは「hello_world_0」プロジェクトを作る感じなのだが、スケルトンがいくつかあるので紹介。

|

スケルトン |

記述 |

|

Dhrystone |

ベンチマークプログラム |

|

Empty Application |

空の C プロジェクト |

|

Hello World |

Let’s say ‘Hello World’ in C. らしい。 |

|

lwIP Echo Server |

lwIP (light-weight IO stack) のデモプログラム!! |

|

Memory Tests |

ハードウェア内のメモリ・リージョンのテスト |

|

Peripheral Tests |

ハードウェア内のすべてのペリフェラルの為の簡単なテストルーチン。 |

|

SREC Bootloader |

non volatile memory (不揮発メモリ)から SREC イメージを読み込むシンプルなブートローダ。 |

|

Xilkernel POSIX Threads Demo |

Xilkernel (ザイリンクスのカーネル?) ベースで複数の POSIX スレッドを動かすデモ。 |

|

Zynq FSBL |

Zynq デバイスの為の First Stage Bootloader(FSBL) |

とりえず今回は [Empty Application] を選んで [Next]

ここもそのまま [Finish]

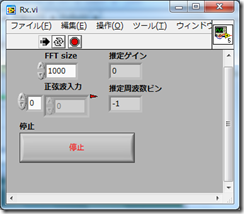

すると中央に情報が表示される。

ターゲット情報

OS情報

周辺回路情報

ライブラリについて

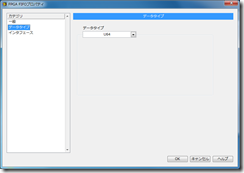

- SDK: Cソースを追加する。

やっと、Cソースを追加することができる。

Project Explorer の [empty_application_0] のしたの [src] にソースを追加する。

[File] → [New] → [Source File]

Source Folder の [Browse] をクリック

src を選んで [OK]

Source File には "main.c"

Template では [Default C SOurce template]

を選んで [Finish]

空の Cソースが作成される。

このファイルに記述していく。

とりあえず、細かい説明は抜きに以下のソースを張り付ける。

|

|

#include "xparameters.h" // Definition Address Space of Board #include "xgpio_l.h"

int main(void) { unsighned int sw_in = 0;

while(1) { // Get push button bit sw_in = XGpio_ReadReg(XPAR_PUSH_BUTTONS_5BITS_BASEADDR,1); // Set LED bit by push button XGpio_WriteReg(XPAR_LEDS_8BITS_BASEADDR,1,sw_in); } }

|

セーブすると、勝手にビルドして elf ファイルが作成される。

- SDK: ボード上で走らせデバッグする

SDK は起動させたまま。

VC707 の JTAG (micro USB) ポートと PC を USB ケーブルで接続。

VC707 の電源を投入。

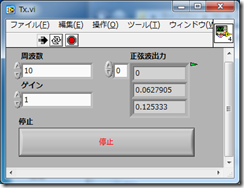

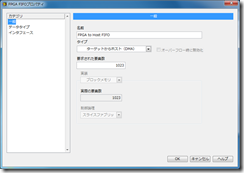

SDK から、FPGA へプログラムを書き込む。

[Xilinx Tools] メニュー → [Program FPGA]

下段の [Software Configuration] の部分を変更する。

ドロップダウンで elf ファイルがあるので、選択。

[Program] ボタン。

プログラム中。。。(JTAG 経由で デバイスははデフォルトで勝手に探してくれる模様)

書き込み終わったら、実行方法を設定。

[Run] メニューの [Run Configurations..]

ダイアログが開くので [Xilinx C/C++ ELF] をダブルクリック。

empty_application_0_Debug というものが追加され、右のペーンで設定ができる。

今回は特になし。

[RUN] ボタン。

これで、実行された。

VC707 上の ボタンで 対応したビットのLED が点灯する。

デバッグする。

一度、停止させる。停止させるには、Console のタブにある

このボタンで停止。

このマークでデバッグモードに入る。

[Yes]

デバッグモードでは SDK の見た目が少し変わる。

ソースにブレイクポイントがかけられる。

変数をウォッチしたり、一通りのデバッグ機能はある。

ここで、ソースをデバッグしたりして、完成したら次のフェーズへ。

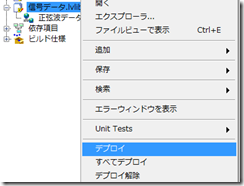

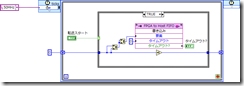

- ISE: MicroBlaze プログラム (elf) を含めて ISE でコンパイルし 最終ビットファイルを作成する。

SDK でプログラム(elf) のデバッグも終わったら終了させる。

ISE に戻り、

Hierarchy で SYSTEM_i をハイライト。

[Project] → [Add Source] で、"SYSTEM\SDK\SDK_Export\empty_application_0\Debug" の下にある elf ファイルを選択。

[OK]

上がシミュレーションで使うか?下が実装するか?のオプション。

通常、どちらもチェックして[OK]

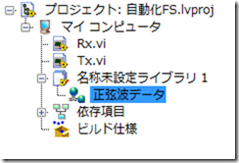

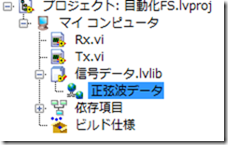

SYSTEM_i の下に elf が追加された。

Hierarchy で SYSTEM_top をハイライト。

新しく elf が追加されたので、[Generate Programming File] が ? マークになっている。

[[Generate Programming File] をダブルクリックして bit ファイルを作成。

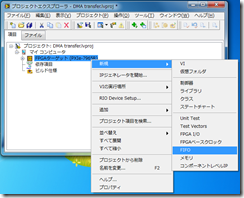

- Impact でダウンロード

ISE で、[Tool] メニューから [IMPACT] を選択。

IMPACT プロジェクトがないのでなんやかんや。

といあえず[OK]しかないので [OK]

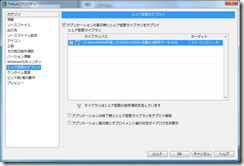

Xilinx へ情報提供。1分といことだが、時間が無いのでまたの機会に。[No]で。

IMPACT の画面。

[Boundary Scan] をダブルクリック。

右のペーンに 「Right click to Add Device or Initialize TAG chain」と出ているので「右クリック」→ [Initialize chain]

コンフィグファイルをアサインしたいので [Yes]

System_top.bit を選択し [Open]

Flash PROM サポートしてるけど、SPI or BPI PROM にアタッチするか?

よく意味がわからないけど、PROM に書き込むか聞いているらしい。

今回は、普通にコンフィグのみなので、No にしておく。

Verify は チェックが入らない。

[OK]

[Program] をダブルクリック。

電源を切ってもう一度。

Baundary Scan -> bit ファイル指定→Program

動作した。

![clip_image001[10] clip_image001[10]](https://dolphinsasoh.files.wordpress.com/2012/09/clip_image00110_thumb.png?w=564&h=352)

![clip_image002[6] clip_image002[6]](https://dolphinsasoh.files.wordpress.com/2012/09/clip_image0026_thumb.png?w=132&h=109)

![clip_image003[6] clip_image003[6]](https://dolphinsasoh.files.wordpress.com/2012/09/clip_image0036_thumb.png?w=1040&h=808)

![clip_image004[6] clip_image004[6]](https://dolphinsasoh.files.wordpress.com/2012/09/clip_image0046_thumb.png?w=219&h=184)

![clip_image005[6] clip_image005[6]](https://dolphinsasoh.files.wordpress.com/2012/09/clip_image0056_thumb.png?w=634&h=561)

![clip_image006[6] clip_image006[6]](https://dolphinsasoh.files.wordpress.com/2012/09/clip_image0066_thumb.png?w=634&h=571)

![clip_image007[6] clip_image007[6]](https://dolphinsasoh.files.wordpress.com/2012/09/clip_image0076_thumb.png?w=581&h=137)

![clip_image008[6] clip_image008[6]](https://dolphinsasoh.files.wordpress.com/2012/09/clip_image0086_thumb.png?w=634&h=571)

![clip_image009[6] clip_image009[6]](https://dolphinsasoh.files.wordpress.com/2012/09/clip_image0096_thumb.png?w=579&h=283)

![clip_image010[6] clip_image010[6]](https://dolphinsasoh.files.wordpress.com/2012/09/clip_image0106_thumb.png?w=386&h=139)

![clip_image011[6] clip_image011[6]](https://dolphinsasoh.files.wordpress.com/2012/09/clip_image0116_thumb.png?w=598&h=481)

![clip_image012[6] clip_image012[6]](https://dolphinsasoh.files.wordpress.com/2012/09/clip_image0126_thumb.png?w=619&h=506)

![clip_image013[6] clip_image013[6]](https://dolphinsasoh.files.wordpress.com/2012/09/clip_image0136_thumb.png?w=1040&h=808)

![clip_image014[6] clip_image014[6]](https://dolphinsasoh.files.wordpress.com/2012/09/clip_image0146_thumb.png?w=506&h=129)

![clip_image015[6] clip_image015[6]](https://dolphinsasoh.files.wordpress.com/2012/09/clip_image0156_thumb.png?w=638&h=494)

![clip_image016[6] clip_image016[6]](https://dolphinsasoh.files.wordpress.com/2012/09/clip_image0166_thumb.png?w=766&h=738)

![clip_image017[6] clip_image017[6]](https://dolphinsasoh.files.wordpress.com/2012/09/clip_image0176_thumb.png?w=768&h=837)

![clip_image018[6] clip_image018[6]](https://dolphinsasoh.files.wordpress.com/2012/09/clip_image0186_thumb.png?w=218&h=100)

![clip_image019[6] clip_image019[6]](https://dolphinsasoh.files.wordpress.com/2012/09/clip_image0196_thumb.png?w=1040&h=806)

![clip_image020[6] clip_image020[6]](https://dolphinsasoh.files.wordpress.com/2012/09/clip_image0206_thumb.png?w=342&h=150)

![clip_image021[6] clip_image021[6]](https://dolphinsasoh.files.wordpress.com/2012/09/clip_image0216_thumb.png?w=409&h=208)

![clip_image022[6] clip_image022[6]](https://dolphinsasoh.files.wordpress.com/2012/09/clip_image0226_thumb.png?w=456&h=193)

![clip_image023[6] clip_image023[6]](https://dolphinsasoh.files.wordpress.com/2012/09/clip_image0236_thumb.png?w=496&h=438)

![clip_image024[6] clip_image024[6]](https://dolphinsasoh.files.wordpress.com/2012/09/clip_image0246_thumb.png?w=445&h=184)

![clip_image027[6] clip_image027[6]](https://dolphinsasoh.files.wordpress.com/2012/09/clip_image0276_thumb.png?w=377&h=224)

![clip_image028[6] clip_image028[6]](https://dolphinsasoh.files.wordpress.com/2012/09/clip_image0286_thumb.png?w=314&h=238)

![clip_image029[6] clip_image029[6]](https://dolphinsasoh.files.wordpress.com/2012/09/clip_image0296_thumb.png?w=427&h=133)

![clip_image030[6] clip_image030[6]](https://dolphinsasoh.files.wordpress.com/2012/09/clip_image0306_thumb.png?w=409&h=171)

![clip_image031[6] clip_image031[6]](https://dolphinsasoh.files.wordpress.com/2012/09/clip_image0316_thumb.png?w=963&h=338)

![clip_image032[6] clip_image032[6]](https://dolphinsasoh.files.wordpress.com/2012/09/clip_image0326_thumb.png?w=1024&h=768)

![clip_image033[6] clip_image033[6]](https://dolphinsasoh.files.wordpress.com/2012/09/clip_image0336_thumb.png?w=674&h=138)

![clip_image034[6] clip_image034[6]](https://dolphinsasoh.files.wordpress.com/2012/09/clip_image0346_thumb.png?w=963&h=799)

![clip_image035[6] clip_image035[6]](https://dolphinsasoh.files.wordpress.com/2012/09/clip_image0356_thumb.png?w=963&h=799)

![clip_image036[6] clip_image036[6]](https://dolphinsasoh.files.wordpress.com/2012/09/clip_image0366_thumb.png?w=768&h=228)

![clip_image037[6] clip_image037[6]](https://dolphinsasoh.files.wordpress.com/2012/09/clip_image0376_thumb.png?w=940&h=167)

![clip_image038[6] clip_image038[6]](https://dolphinsasoh.files.wordpress.com/2012/09/clip_image0386_thumb.png?w=390&h=195)

![clip_image039[6] clip_image039[6]](https://dolphinsasoh.files.wordpress.com/2012/09/clip_image0396_thumb.png?w=371&h=120)

![clip_image040[6] clip_image040[6]](https://dolphinsasoh.files.wordpress.com/2012/09/clip_image0406_thumb.png?w=587&h=243)

![clip_image041[6] clip_image041[6]](https://dolphinsasoh.files.wordpress.com/2012/09/clip_image0416_thumb.png?w=963&h=500)

![clip_image042[6] clip_image042[6]](https://dolphinsasoh.files.wordpress.com/2012/09/clip_image0426_thumb.png?w=255&h=164)

![clip_image043[6] clip_image043[6]](https://dolphinsasoh.files.wordpress.com/2012/09/clip_image0436_thumb.png?w=465&h=363)

![clip_image044[6] clip_image044[6]](https://dolphinsasoh.files.wordpress.com/2012/09/clip_image0446_thumb.png?w=266&h=163)

![clip_image045[6] clip_image045[6]](https://dolphinsasoh.files.wordpress.com/2012/09/clip_image0456_thumb.png?w=963&h=392)

![clip_image046[6] clip_image046[6]](https://dolphinsasoh.files.wordpress.com/2012/09/clip_image0466_thumb.png?w=819&h=126)

![clip_image047[6] clip_image047[6]](https://dolphinsasoh.files.wordpress.com/2012/09/clip_image0476_thumb.png?w=933&h=233)

![clip_image048[6] clip_image048[6]](https://dolphinsasoh.files.wordpress.com/2012/09/clip_image0486_thumb.png?w=184&h=220)

![clip_image049[6] clip_image049[6]](https://dolphinsasoh.files.wordpress.com/2012/09/clip_image0496_thumb.png?w=270&h=328)

![clip_image050[6] clip_image050[6]](https://dolphinsasoh.files.wordpress.com/2012/09/clip_image0506_thumb.png?w=273&h=319)

![clip_image001[11] clip_image001[11]](https://dolphinsasoh.files.wordpress.com/2012/09/clip_image00111_thumb.png?w=564&h=352)

![clip_image051[6] clip_image051[6]](https://dolphinsasoh.files.wordpress.com/2012/09/clip_image0516_thumb.png?w=102&h=71)

![clip_image052[6] clip_image052[6]](https://dolphinsasoh.files.wordpress.com/2012/09/clip_image0526_thumb.png?w=74&h=56)

![clip_image053[6] clip_image053[6]](https://dolphinsasoh.files.wordpress.com/2012/09/clip_image0536_thumb.png?w=923&h=255)

![clip_image054[6] clip_image054[6]](https://dolphinsasoh.files.wordpress.com/2012/09/clip_image0546_thumb.png?w=1317&h=928)

![clip_image055[6] clip_image055[6]](https://dolphinsasoh.files.wordpress.com/2012/09/clip_image0556_thumb.png?w=446&h=232)

![clip_image056[6] clip_image056[6]](https://dolphinsasoh.files.wordpress.com/2012/09/clip_image0566_thumb.png?w=155&h=133)

![clip_image057[6] clip_image057[6]](https://dolphinsasoh.files.wordpress.com/2012/09/clip_image0576_thumb.png?w=496&h=438)

![clip_image058[6] clip_image058[6]](https://dolphinsasoh.files.wordpress.com/2012/09/clip_image0586_thumb.png?w=716&h=410)

![clip_image059[6] clip_image059[6]](https://dolphinsasoh.files.wordpress.com/2012/09/clip_image0596_thumb.png?w=431&h=165)

![clip_image060[6] clip_image060[6]](https://dolphinsasoh.files.wordpress.com/2012/09/clip_image0606_thumb.png?w=426&h=162)

![clip_image061[6] clip_image061[6]](https://dolphinsasoh.files.wordpress.com/2012/09/clip_image0616_thumb.png?w=249&h=223)

![clip_image062[6] clip_image062[6]](https://dolphinsasoh.files.wordpress.com/2012/09/clip_image0626_thumb.png?w=265&h=197)

![clip_image063[6] clip_image063[6]](https://dolphinsasoh.files.wordpress.com/2012/09/clip_image0636_thumb.png?w=178&h=283)

![clip_image064[6] clip_image064[6]](https://dolphinsasoh.files.wordpress.com/2012/09/clip_image0646_thumb.png?w=506&h=205)

![clip_image065[6] clip_image065[6]](https://dolphinsasoh.files.wordpress.com/2012/09/clip_image0656_thumb.png?w=506&h=129)

![clip_image066[6] clip_image066[6]](https://dolphinsasoh.files.wordpress.com/2012/09/clip_image0666_thumb.png?w=1040&h=806)

![clip_image067[6] clip_image067[6]](https://dolphinsasoh.files.wordpress.com/2012/09/clip_image0676_thumb.png?w=165&h=184)

![clip_image068[6] clip_image068[6]](https://dolphinsasoh.files.wordpress.com/2012/09/clip_image0686_thumb.png?w=321&h=216)

![clip_image069[6] clip_image069[6]](https://dolphinsasoh.files.wordpress.com/2012/09/clip_image0696_thumb.png?w=458&h=133)

![clip_image070[6] clip_image070[6]](https://dolphinsasoh.files.wordpress.com/2012/09/clip_image0706_thumb.png?w=674&h=450)

![clip_image071[6] clip_image071[6]](https://dolphinsasoh.files.wordpress.com/2012/09/clip_image0716_thumb.png?w=189&h=164)

![clip_image072[6] clip_image072[6]](https://dolphinsasoh.files.wordpress.com/2012/09/clip_image0726_thumb.png?w=416&h=129)

![clip_image073[6] clip_image073[6]](https://dolphinsasoh.files.wordpress.com/2012/09/clip_image0736_thumb.png?w=716&h=410)

![clip_image074[6] clip_image074[6]](https://dolphinsasoh.files.wordpress.com/2012/09/clip_image0746_thumb.png?w=269&h=195)

![clip_image075[6] clip_image075[6]](https://dolphinsasoh.files.wordpress.com/2012/09/clip_image0756_thumb.png?w=272&h=77)

![clip_image001[4] clip_image001[4]](https://dolphinsasoh.files.wordpress.com/2012/03/clip_image0014_thumb.png?w=244&h=162)

![clip_image002[4] clip_image002[4]](https://dolphinsasoh.files.wordpress.com/2012/03/clip_image0024_thumb.png?w=244&h=68)

![clip_image003[4] clip_image003[4]](https://dolphinsasoh.files.wordpress.com/2012/03/clip_image0034_thumb.png?w=244&h=71)

![clip_image004[4] clip_image004[4]](https://dolphinsasoh.files.wordpress.com/2012/03/clip_image0044_thumb.png?w=244&h=70)

![clip_image005[4] clip_image005[4]](https://dolphinsasoh.files.wordpress.com/2012/03/clip_image0054_thumb.png?w=244&h=72)

![clip_image006[4] clip_image006[4]](https://dolphinsasoh.files.wordpress.com/2012/03/clip_image0064_thumb.png?w=244&h=71)

![clip_image008[4] clip_image008[4]](https://dolphinsasoh.files.wordpress.com/2012/03/clip_image0084_thumb.png?w=244&h=68)

![clip_image009[4] clip_image009[4]](https://dolphinsasoh.files.wordpress.com/2012/03/clip_image0094_thumb.png?w=244&h=68)

![clip_image010[4] clip_image010[4]](https://dolphinsasoh.files.wordpress.com/2012/03/clip_image0104_thumb.png?w=244&h=69)

![clip_image011[4] clip_image011[4]](https://dolphinsasoh.files.wordpress.com/2012/03/clip_image0114_thumb.png?w=244&h=152)

![clip_image012[4] clip_image012[4]](https://dolphinsasoh.files.wordpress.com/2012/03/clip_image0124_thumb.png?w=244&h=69)

![clip_image013[4] clip_image013[4]](https://dolphinsasoh.files.wordpress.com/2012/03/clip_image0134_thumb.png?w=244&h=70)